You're now following

Error following user.

This user does not allow users to follow them.

You are already following this user.

Your membership plan only allows 0 follows. Upgrade here.

Successfully unfollowed

Error unfollowing user.

You have successfully recommended

Error recommending user.

Something went wrong. Please refresh the page and try again.

Email successfully verified.

alexandria, egypt

It's currently 12:53 PM here

Joined December 7, 2022

0 Recommendations

Mohamed M.

@Majiidd

0.0

0.0

100%

100%

alexandria, egypt

N/A

Jobs Completed

N/A

On Budget

N/A

On Time

N/A

Repeat Hire Rate

Verilog/SV/VHDL RTL coding | FPGA | ASIC | VLSI

Contact Mohamed M. about your job

Log in to discuss any details over chat.

Portfolio

Portfolio

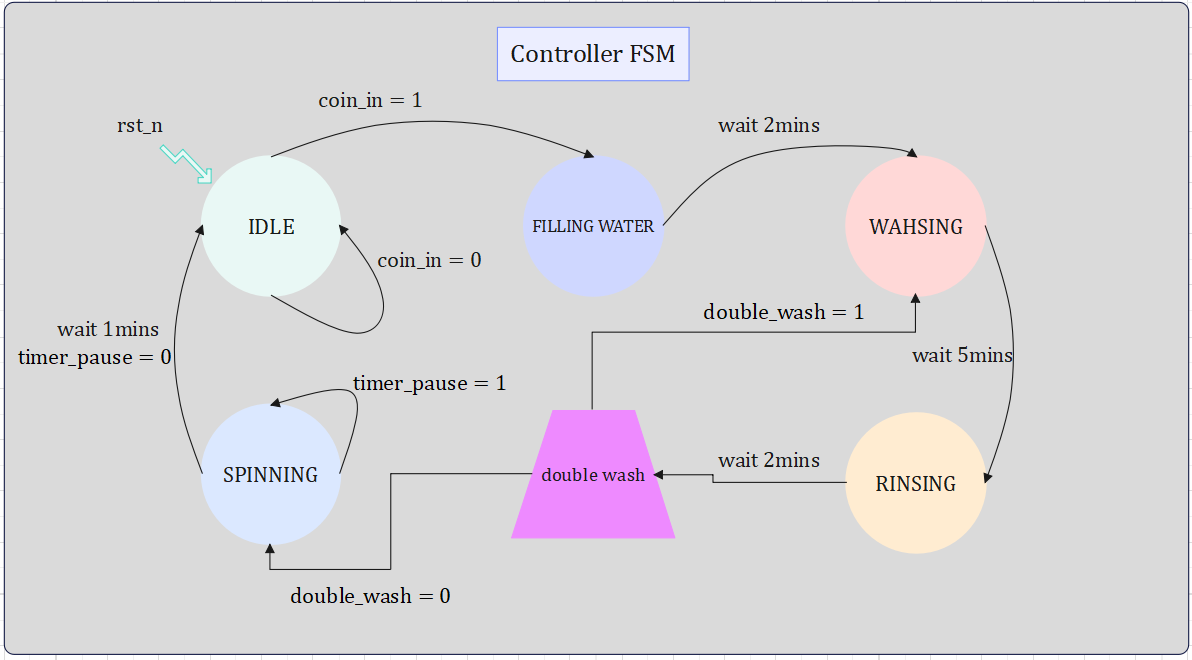

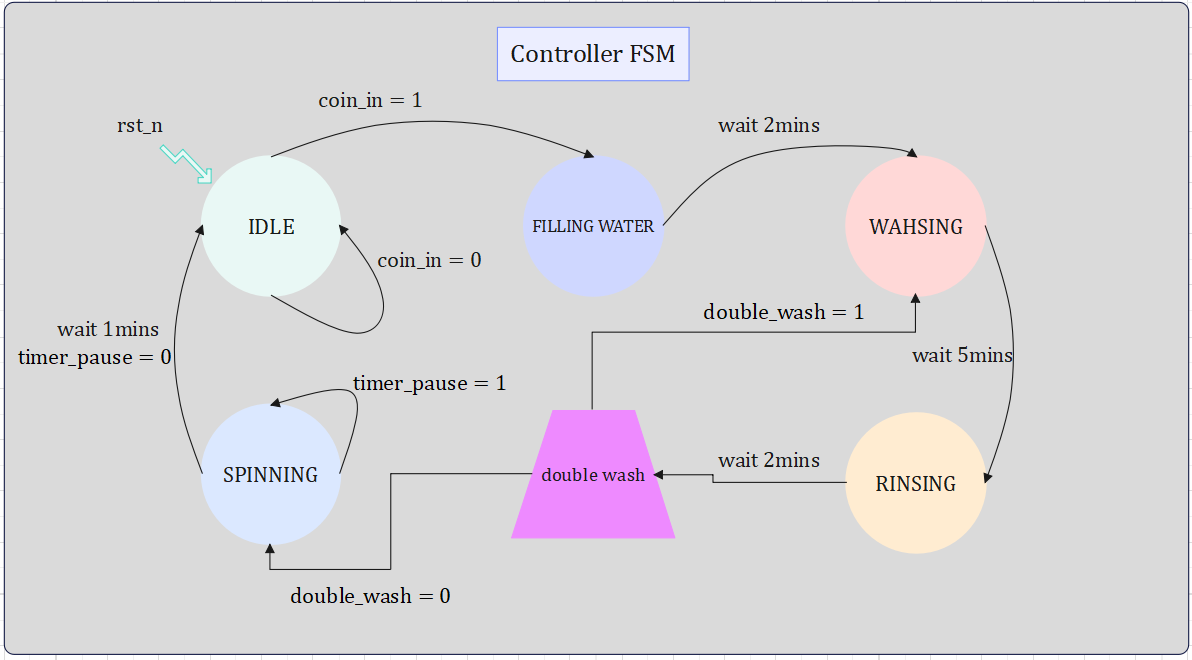

Washing Machine Controller, using Verilog HDL.

Washing Machine Controller, using Verilog HDL.

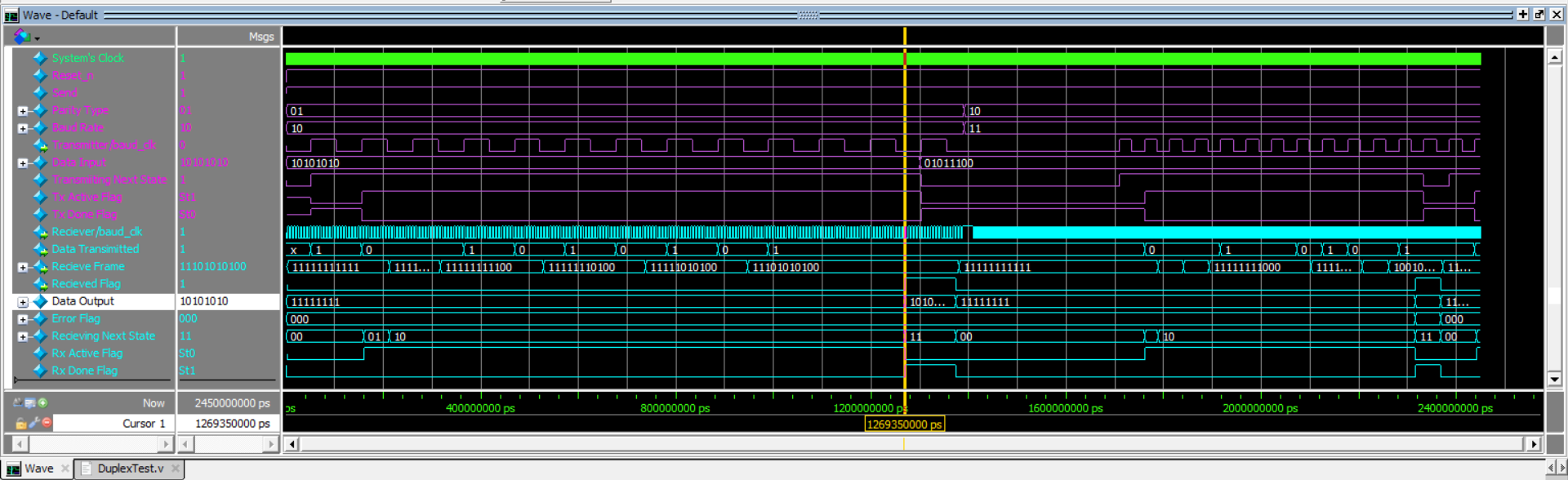

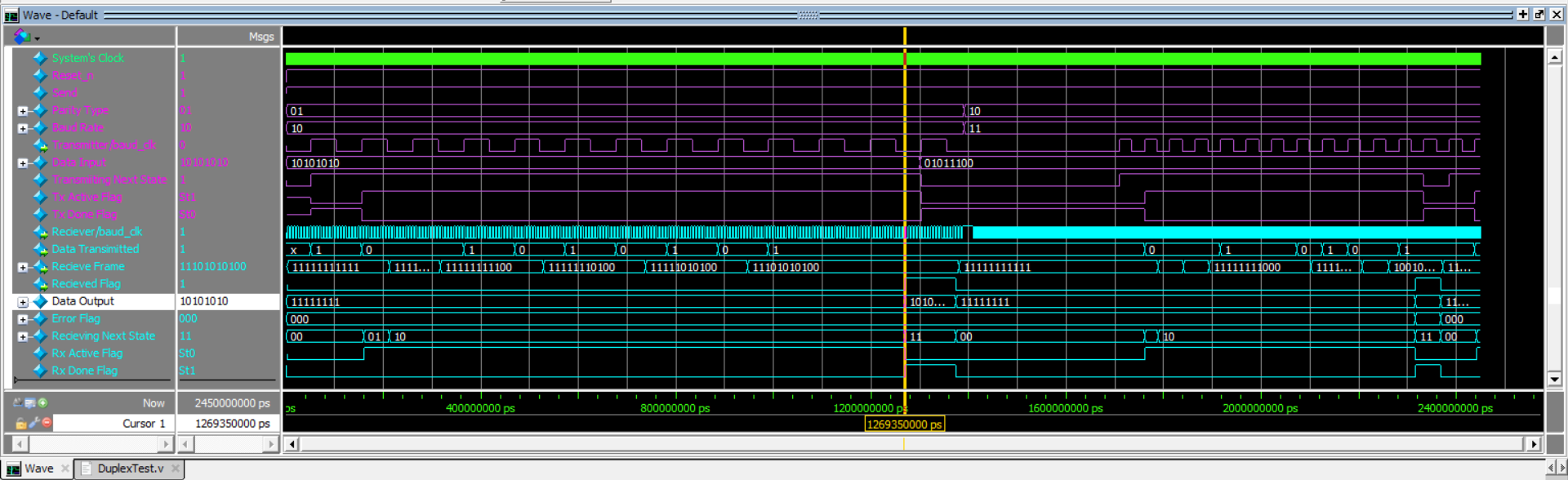

Full UART implementation using Verilog HDL

Full UART implementation using Verilog HDL

Full UART implementation using Verilog HDL

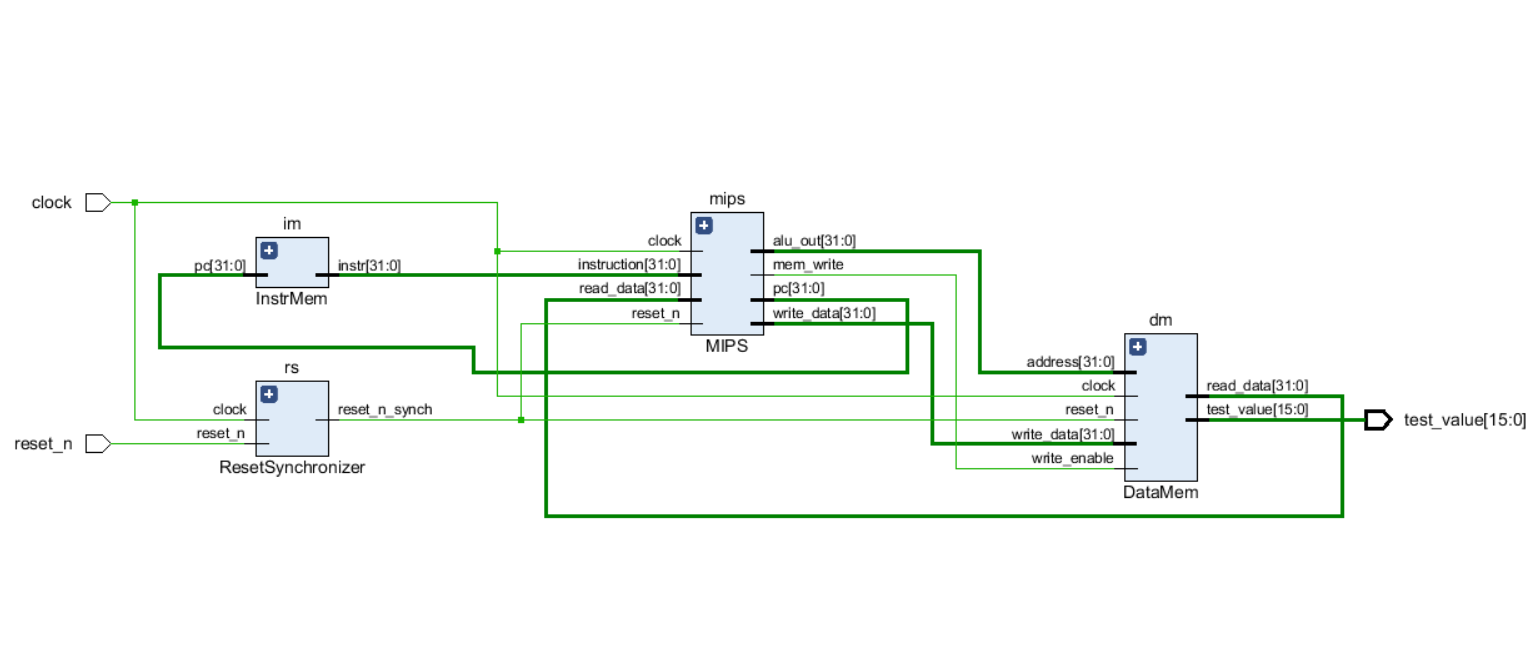

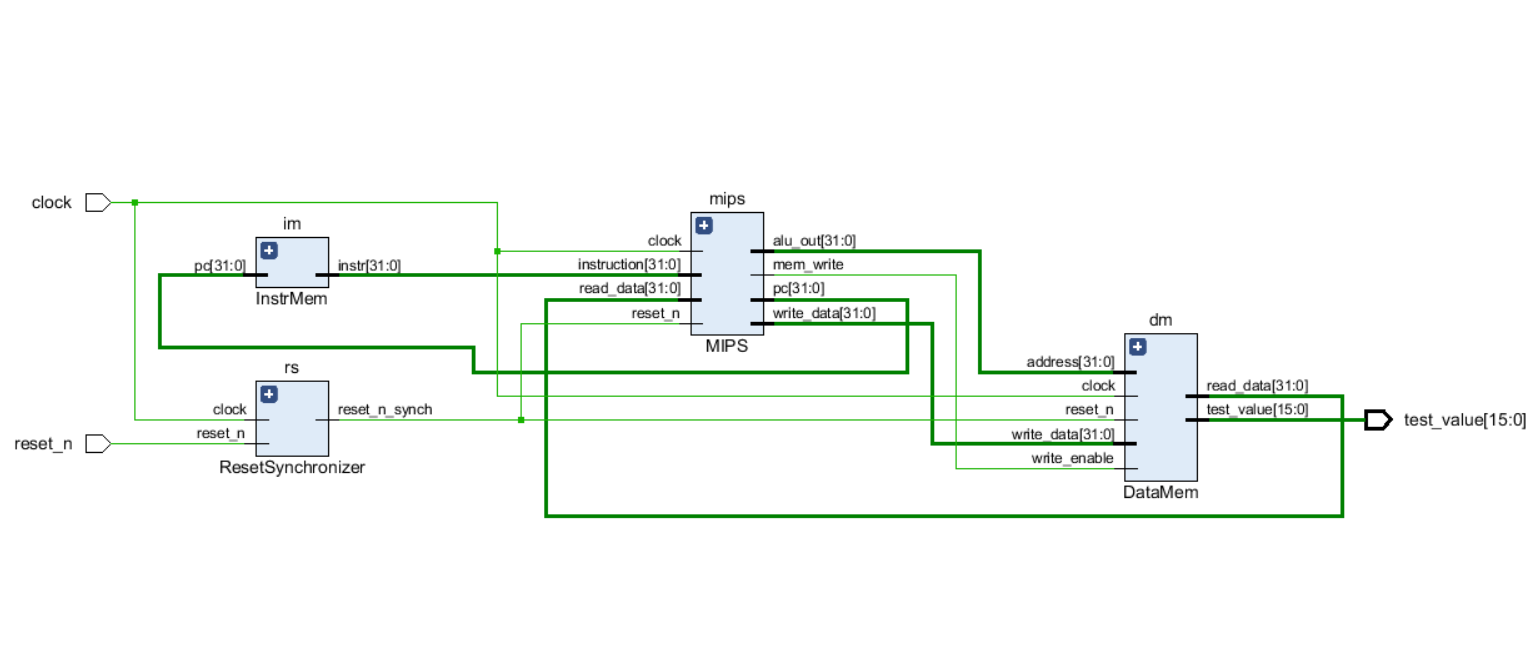

Implementation of 32-bit MIPS-processor using SystemVerilog

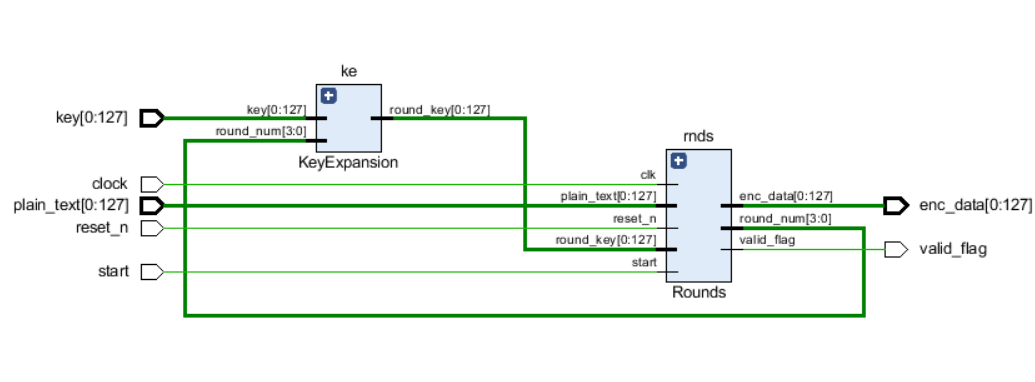

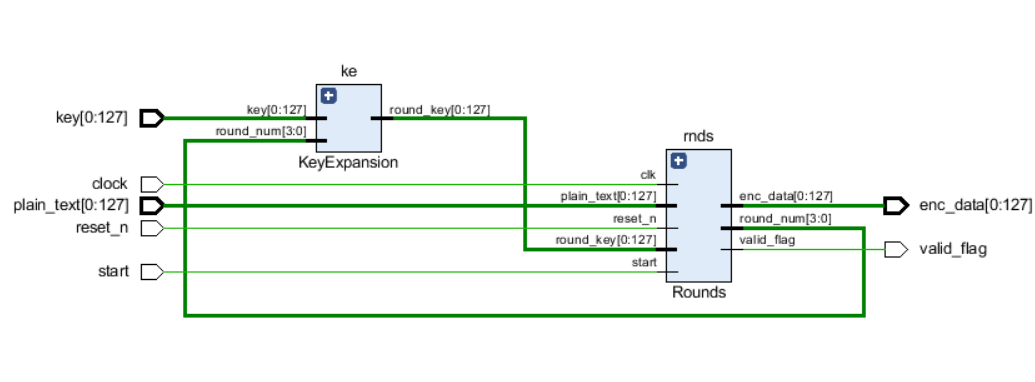

Advanced Encryption Standard (AES) modelling, using Verilog

Washing Machine Controller, using Verilog HDL.

Washing Machine Controller, using Verilog HDL.

Full UART implementation using Verilog HDL

Full UART implementation using Verilog HDL

Full UART implementation using Verilog HDL

Implementation of 32-bit MIPS-processor using SystemVerilog

Advanced Encryption Standard (AES) modelling, using Verilog

Reviews

Changes saved

No reviews to see here!

Experience

Digital IC Design and Verfication

Mar 2022 - Present

◦ Efficient Synthesizable RTL coding: using Verilog/SystemVerilog HDLs

◦ Computer Architecture: Undersatnding of the under-hood of the computer by studying the MIPS processor architecture

and designing it by SystemVerilog HDL.

◦ Verification: Understanding of the basic concepts of verification using SystemVerilog HDL.

Digital IC Design with FPGA

Aug 2022 - Nov 2022 (3 months, 1 day)

◦ Efficient Synthesizable RTL coding: using Verilog HDL, Self-test test benches.

◦ Synthesis and implementation: used Xilinx ISE to implement the design on Spartan-6, I/O

planning layout using the PlanAhead tool, tested the design with multiple clock domains and applied to time

constraints.

◦ Acceleration FPGA Design: used Vivado IDE to implement the design on the Zynq-7000 board, used the logic analyzer to debug the design and created IP then used the IP integrator to create a block design.

Education

Bachelor degree of Electronics and Electrical Communication Engineering

(4 years)

Qualifications

Digital Design with FPGA

NajahNow, One Lab, Zewail City

2022

- Efficient Synthesizable RTL coding: using Verilog HDL, verified by Self-test test-benches.

- HDL Synthesis and implementation on FPGA: used Xilinx ISE to implement the design on Spartan-6 FPGA, I/O planning layout for pin assignment using PlanAhead tool, tested the design with multiple clock domains, and applied timing constraints.

- Acceleration FPGA Design: used Vivado IDE to implement the design on the Zynq-7000 board.

Contact Mohamed M. about your job

Log in to discuss any details over chat.

Verifications

Browse Similar Freelancers

Browse Similar Showcases

Invite sent successfully!

Thanks! We’ve emailed you a link to claim your free credit.

Something went wrong while sending your email. Please try again.

Loading preview

Permission granted for Geolocation.

Your login session has expired and you have been logged out. Please log in again.